TL;DR:

- Demand for localized data-centric intelligence is growing, fueling the rise of edge-AI devices.

- The von Neumann bottleneck poses challenges for memory-bound AI tasks.

- In-memory computing (IMC) with multi-bit MAC operations is a game-changer.

- The innovative IMC crossbar macro with FeFET cells overcomes binary limitations.

- Achieves remarkable accuracy in handwriting recognition and image classification.

- Boasts an energy efficiency rating of 885.4 TOPS/W, nearly double existing designs.

Main AI News:

In a world where the demand for localized data-driven intelligence is burgeoning, the imperative of empowering devices to autonomously analyze data at the edge has never been more pronounced. The ascent of edge-AI devices, spanning wearables, sensors, smartphones, and automobiles, marks the next evolutionary phase in the semiconductor domain. These devices embody real-time learning, autonomy, and embedded intelligence.

Yet, this ascent is not without its challenges, primarily encapsulated in the von Neumann bottleneck. This bottleneck, a formidable hurdle, arises from memory-bound computational tasks, particularly in the realms of deep learning and AI, which often require data access that exceeds the capabilities of traditional algorithmic logic units.

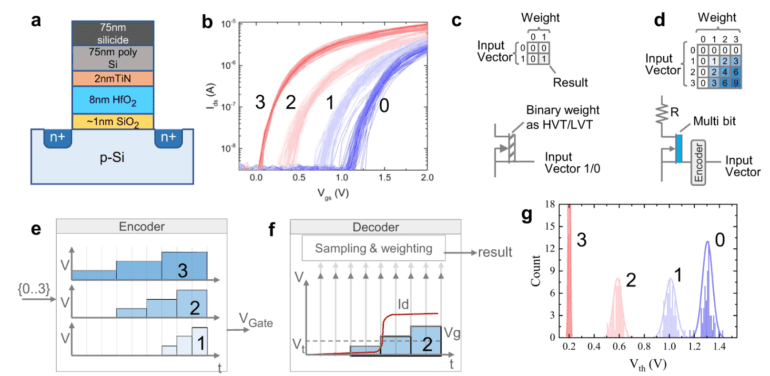

In the quest to overcome this computational impasse, we have witnessed the emergence of architectural innovations, most notably in-memory computing (IMC). IMC, by executing Multiply and Accumulate (MAC) operations directly within the memory array, holds the potential to revolutionize AI systems. However, conventional implementations of IMC have been constrained by their focus on binary logical operations, limiting their effectiveness in handling more intricate computations.

Enter the groundbreaking in-memory computing (IMC) crossbar macro, featuring a multi-level ferroelectric field-effect transistor (FeFET) cell designed for multi-bit MAC operations. This pioneering innovation transcends the confines of conventional binary operations, harnessing the electrical attributes of stored data within memory cells to yield MAC operation results encoded in activation time and cumulative current.

The performance benchmarks achieved by this innovation are nothing short of extraordinary. With an astonishing 96.6% accuracy in handwriting recognition and an impressive 91.5% accuracy in image classification, all achieved without additional training, this solution is poised to reshape the landscape of AI. Its energy efficiency, rated at an impressive 885.4 TOPS/W, nearly doubles that of existing designs, reaffirming its potential to propel the industry to new heights.

Conclusion:

This breakthrough chip’s integration of processing and memory heralds a new era in AI efficiency. Its ability to tackle memory-bound tasks with exceptional accuracy and energy efficiency positions it as a game-changer in the market, poised to drive the semiconductor and AI industries forward.